# 国家 IP 核标准符合性评测与认证指南 (v1.0)

集成电路公共服务部 信息产业部软件与集成电路促进中心

# 目录

| <b>一</b> 、 |      | IP 核评测与认证流程              | 3  |

|------------|------|--------------------------|----|

| _,         |      | IP 核评测与认证类别              | 4  |

|            | 1.   | 数字软 IP 核标准符合度验证评测(类别一)   | 4  |

|            |      | 1) 流程                    | 4  |

|            |      | 2) 度量定义                  | 4  |

|            |      | 3) 评测输出                  | 4  |

|            | 2.   | 数字软 IP 核 EDA 工具验证评测(类别二) | 5  |

|            |      | 1) 流程                    | 5  |

|            |      | 2) 度量定义                  | 6  |

|            |      | 3) 评测输出                  | 9  |

|            |      | a) 代码质量检查报告              | 9  |

|            |      | b) 验证质量检查报告              | 10 |

|            |      | c) 综合质量检查报告              | 10 |

|            |      | d) 可测性检查报告               | 11 |

|            |      | e) 形式化验证报告               | 11 |

|            |      | f) 性能检查报告                | 11 |

|            |      | g) 功耗检查报告                | 12 |

|            | 3.   | 数字软 IP 核 FPGA 验证评测(类别三)  | 13 |

|            |      | 1) 流程                    | 13 |

|            |      | 2) 度量定义                  | 14 |

|            |      | 3) 评测输出                  | 15 |

|            | 4.   | 数字软 IP 核硅形态验证评测(类别四)     | 16 |

|            |      | 1) 流程                    | 16 |

|            |      | 2) 度量定义                  | 16 |

|            |      | 3) 评测输出                  | 17 |

| 三、         |      | 附件一(申请书)                 | 18 |

|            | 填え   | 表要求                      | 19 |

|            | 申请   | 请单位基本情况                  | 20 |

|            | IP ₹ | 核概况                      | 21 |

|            | 申请   | 请单位声明                    | 22 |

| 四、         |      | 附件二                      | 23 |

|            | 数与   | 字软 IP 交付项                | 23 |

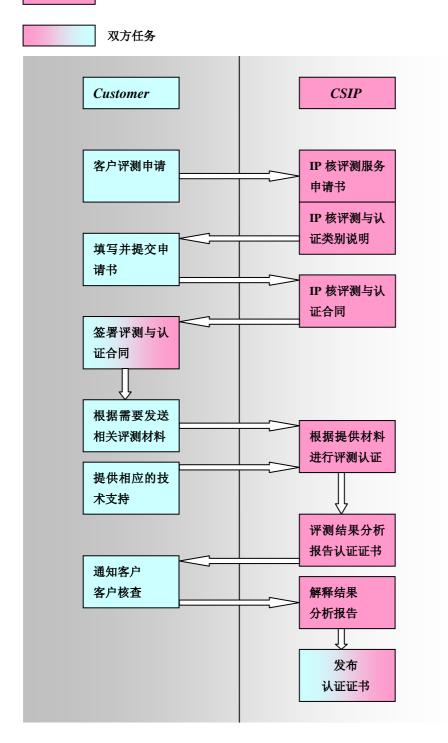

# 一、 IP 核评测与认证流程

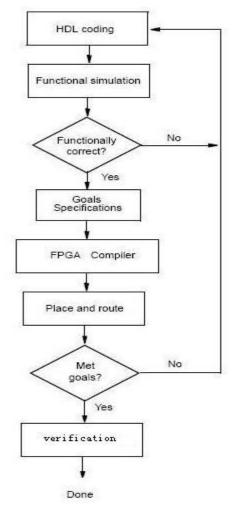

### IP 核评测与认证流程

客户任务

CSIP 任务

## 二、IP核评测与认证类别

对于数字软 IP 核的评测与认证将采取四种方法进行,分别为:

- 1、数字软 IP 核标准符合度验证评测;

- 2、数字软 IP 核 EDA 工具验证评测;

- 3、数字软 IP 核 FPGA 验证评测;

- 4、 数字软 IP 核硅形态验证评测。

以上四种方法从不同侧面和角度对数字软 IP 核进行评测与认证,详见下面具体说明。 评测申请单位在填写附件一的申请书时,需要根据需求参看下面的说明填写出详细需求 验证评测类别。

#### 1. 数字软 IP 核标准符合度验证评测 (类别一)

#### 1) 流程

客户依照《IP 核评测交付项列表》(参见附录二),提供给 CSIP 相应的数据和文档。评测人员完成对 IP 核交付项的整理和分析后,交付到评测系统。评测系统依照度量定义并结合相应的权值给出 IP 核评分。

#### 2) 度量定义

依据信息产业部《集成电路 IP 核测试数据交换格式和准则规范》等 11 项标准作为基础,在以下几个方面对评测 IP 核给出综合的评价:交付项清单、代码质量、系统质量、逻辑设计、测试和制造质量、功能验证、时序和功耗质量等几个方面。

#### 3) 评测输出

在对客户 IP 核全方位、细致评测的基础上,我们依据国家 IP 核标准,通过我们的评测系统给出该 IP 核的评分。分值的高低反映了 IP 核在各方面与标准的符合度。

| 摘要                                          |                                       |                |                      |                |

|---------------------------------------------|---------------------------------------|----------------|----------------------|----------------|

| 软核IP的质量等级为                                  |                                       | Some deliveral | ole items are no     | t answered     |

| 总分                                          |                                       |                |                      |                |

| 未回答的度量问题数                                   |                                       |                |                      | 202            |

| 未回答的可交付项数                                   |                                       |                |                      | 49             |

| 5.0                                         |                                       |                |                      |                |

| 度量问题                                        | 满足                                    | 不满足            | 百分比                  | 未答             |

| Fatal度量问题                                   | n.                                    | 0              | 0.0%                 | 11             |

| ratal)文里门处                                  | · · · · · · · · · · · · · · · · · · · |                |                      |                |

| Fatal及星门巡<br>Imperative度量问题                 | 0                                     | 0              | 0.0%                 |                |

|                                             | 0                                     | 0              |                      | 31             |

| Imperative度量问题                              | 0<br>0<br>0                           | 0;<br>0;<br>0; | 0.0%                 | 37<br>78<br>76 |

| Imperative度量问题<br>Rule度量问题                  |                                       |                | 0.0%<br>0.0%         | 31<br>78<br>76 |

| Imperative度量问题<br>Rule度量问题<br>Guideline度量问题 | 0<br>0<br>0<br>0<br>0<br>0<br>0       | 未提供            | 0.0%<br>0.0%<br>0.0% | 37<br>78       |

## 2. 数字软 IP 核 EDA 工具验证评测(类别二)

#### 1) 流程

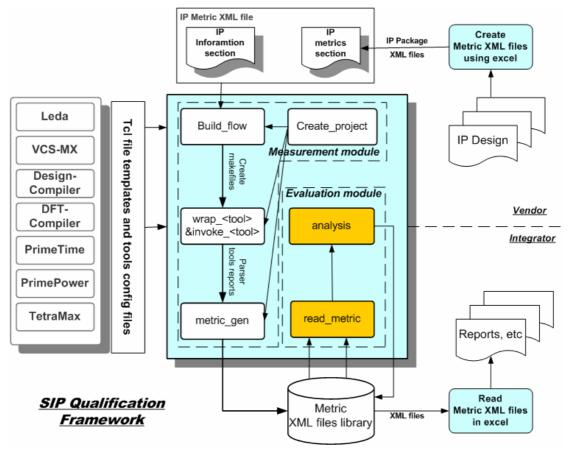

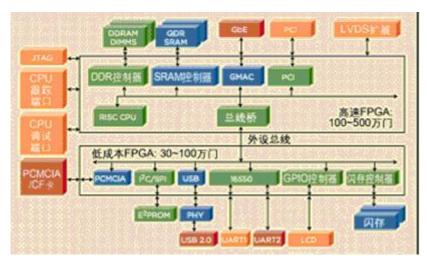

整个 IP 评测框架的目标是辅助评估人员对 IP 作出准确的评估。目前该框架被设计为支持 Verilog 或是 VHDL 描述的软核 IP。图 1 给出了整个评估框架的体系结构,以及关键的组件。

图 1 数字软 IP 核评测框图

## 2) 度量定义

目前该评测框架中使用的度量都定义在表 1 中。为了完成该度量的测量过程所需要的可交付项也同时列出。为了完成一个完整的 IP 质量评测流程,这些所需的可交付项必须包括在 IP 的最终的交付包中。

|                                         | 衣 I 剱子软 IP 核及重定义衣                      |                      |

|-----------------------------------------|----------------------------------------|----------------------|

| 度量名称                                    | 说明                                     | 相关的交付项               |

| 代码质量度量                                  |                                        |                      |

| Compliance to VSIA QIP 2.0 coding style | 测量该IP的代码检查中和VSIA QIP 2.0 中定义的代码规则的违反数量 | 可综合的 RTL 代码          |

| Compliance to Readability coding style  | 测量该 IP 的代码检查中和代码可读性<br>中定义的代码规则的违反数量   | 可综合的 RTL 代码          |

| Compliance to DFT rules                 | 测量该 IP 的代码检查中和代码可测性<br>中定义的代码规则的违反数量   | 可综合的 RTL 代码          |

| 设计质量度量                                  |                                        |                      |

| Total Cell Area                         | 计算用于实现逻辑功能的单元总面积                       | 可综合的 RTL 代码,<br>设计约束 |

| Net Interconnection Area                | 计算所有用于实现互连功能的单元的<br>总面积                | 可综合的 RTL 代码,<br>设计约束 |

表 1 数字软 IP 核度量定义表

|                                     |                                                                                    | <b>上竹百住厅侧马队吐指用</b>               |

|-------------------------------------|------------------------------------------------------------------------------------|----------------------------------|

| Total Cell Gate Counts              | 基于逻辑单元总面积和逻辑门的标准<br>面积计算逻辑功能部分的门数,公式如<br>下:<br>Gate Counts = Cell Area/Metric Gate | 可综合的 RTL 代码,<br>设计约束             |

|                                     | Area                                                                               |                                  |

| Net Interconnection Gate<br>Counts  | 基于互连单元总面积和逻辑门的标准<br>面积计算实现互连功能部分的门数,公<br>式如下:<br>Gate Counts = Interconnection     | 可综合的 RTL 代码,<br>设计约束             |

| -1 (>                               | Area/Metric Gate Area                                                              |                                  |

| 验证质量度量                              |                                                                                    |                                  |

| Failing compare points              | 计算在 RTL 级和门级网表之间做形式<br>化验证时所出现的验证失败的比较点<br>数量。                                     | 可综合的 RTL 代码                      |

| Functional Coverage                 | 基于用户提供的包含的断言的功能验<br>证平台计算 IP 的功能覆盖率。该度量目<br>前只是作为一个参考。                             | 测试平台 (包括了断言,声明),验证向量,可综合的 RTL 代码 |

| 代码覆盖率                               |                                                                                    |                                  |

| Statement Coverage                  | 计算在 RTL 级的验证过程中的代码行<br>覆盖率。只有当所有的语句都被测试到<br>的时候,该度量才能达到 100%。                      | 测试平台,验证向量,可综合的 RTL 代码            |

| Branch Coverage                     | 只有当 IP 的代码中所有的 if-then-else 分支语句或是 case 语句被至少一个测试实例所测试到,该度量值才能达到 100%              | 测试平台,验证向量,可综合的 RTL 代码            |

| Condition Coverage                  | 只有当代码中的每一个控制变量能够<br>取到该控制变量的数据类型所允许的<br>所有值时,该度量值才能达到 100%。                        | 测试平台,验证向量,可综合的 RTL 代码            |

| Toggle Coverage                     | 该度量强调的是代码的可控制性问题,<br>大多被用于 RTL 级的数据路径的测试<br>中。                                     | 测试平台,验证向量,可综合的 RTL 代码            |

| FSM transition Coverage             | 该度量用于测量状态机的属性,用于强调在 IP 中的控制逻辑的可能存在的问题。                                             | 测试平台,验证向量,可综合的 RTL 代码            |

| Path Coverage                       | 只有当所有可能的输出都能被一个或<br>多个输入来进行修改时,该度量值才能<br>达到 100%。                                  | 测试平台,验证向量,可综合的 RTL 代码            |

| 时序、性能度量                             |                                                                                    |                                  |

| 时序约束                                |                                                                                    |                                  |

| Typical application clock frequency | 在完成逻辑综合后,计算大概的时钟频率。                                                                | 时序分析脚本                           |

| 时序覆盖率                               |                                                                                    |                                  |

| Setup Time Coverage                 | 该度量是在逻辑综合后的时序分析过                                                                   | 时序分析脚本                           |

|                                     |                                                                                    |                                  |

| _                           |                                        |                       |

|-----------------------------|----------------------------------------|-----------------------|

|                             | 程中计算。强调对信号的建立时间的检                      |                       |

|                             | 查。计算公式如下:                              |                       |

|                             | Setup Time Coverage = violation        |                       |

|                             | numbers of setup timing checking/total |                       |

|                             | numbers of setup timing checking       |                       |

| Hold Time Coverage          | 该度量是在逻辑综合后的时序分析过                       | 时序分析脚本                |

|                             | 程中计算。强调对信号的保持时间的检                      | 4,4,74,614,1          |

|                             | 查。计算公式如下:                              |                       |

|                             | Hold Time Coverage = violation         |                       |

|                             | numbers of hold timing checking/total  |                       |

|                             | numbers of hold timing checking        |                       |

| Min_Pulse_Width Coverage    | 该度量是在逻辑综合后的时序分析过                       | 时序分析脚本                |

| wini_i disc_widiii coverage | 程中计算。强调对信号的持续时间的检                      | H1/1 /1 // 1/1/1/4/4- |

|                             | 查。计算公式如下:                              |                       |

|                             | Min_Pulse_Width Coverage = violation   |                       |

|                             | numbers of min pulse width timing      |                       |

|                             | checking/total numbers of min pulse    |                       |

|                             | width timing checking                  |                       |

|                             | width thining checking                 |                       |

|                             | 该度量是在逻辑综合后的时序分析过                       | 中京八托冊末                |

| Recovery Time Coverage      |                                        | 时序分析脚本                |

|                             | 程中计算,强调对异步的清除和复位信                      |                       |

|                             | 号的时序的检查。计算公式如下:                        |                       |

|                             | Recovery Time Coverage = violation     |                       |

|                             | numbers of recovery timing             |                       |

|                             | checking/total numbers of recovery     |                       |

|                             | timing checking                        | ore A tento 1.        |

| Removal Time Coverage       | 该度量是在逻辑综合后的时序分析过                       | 时序分析脚本                |

|                             | 程中计算,强调对异步的清除和复位信                      |                       |

|                             | 号的时序的检查。计算公式如下:                        |                       |

|                             | Removal Time Coverage = violation      |                       |

|                             | numbers of removal timing              |                       |

|                             | checking/total numbers of removal      |                       |

|                             | timing checking                        | t i Na di tambini di  |

| Timing Borrow Paths         | 统计所有的包括了 latch 的时序路径的                  | 时序分析脚本                |

|                             | 数目。                                    |                       |

|                             | 该度量有助于衡量 IP 的时序分析的复                    |                       |

|                             | 杂度。                                    |                       |

| Multicycle Paths            | 统计所有的包括了多个时钟周期的时                       | 时序分析脚本                |

|                             | 序路径的数目。                                |                       |

|                             | 该度量有助于衡量 IP 的时序分析的复                    |                       |

|                             | 杂度。                                    |                       |

| False Paths                 | 统计所有的假的时序路径的数目。                        | 时序分析脚本                |

|                             | 该度量有助于衡量 IP 的时序分析的复                    |                       |

|                             |                                        |                       |

|                                      | 杂度。                                                     |                       |

|--------------------------------------|---------------------------------------------------------|-----------------------|

| 功耗度量                                 |                                                         |                       |

| ATPG Test Patterns Peak Power        | 基于 ATPG 测试向量来计算峰值功耗。<br>该度量值会随着对工具配置的不同而<br>有较大的变化。     | 功耗分析脚本                |

| Application Test Patterns Peak Power | 基于 IP 供应商提供的测试向量来计算<br>峰值功耗。该度量值会随着对工具配置<br>的不同而有较大的变化。 | 功耗分析脚本                |

| ATPG 测试向量下的平均功耗                      |                                                         |                       |

| Dynamic Average Power                | 基于 ATPG 测试向量来计算动态的平均功耗。                                 | 功耗分析脚本                |

| Static Average Power                 | 基于 ATPG 测试向量来计算静态的平均 功耗。<br>该度量适用于 0.13 微米或以下的工艺<br>流程。 | 功耗分析脚本                |

| 实际测试向量下的平均功耗                         |                                                         |                       |

| Dynamic Average Power                | 基于 IP 供应商提供的测试向量来计算<br>动态的平均功耗                          | 功耗分析脚本                |

| Static Average Power                 | 基于 IP 供应商提供的测试向量来计算静态的平均功耗。<br>该度量适用于 0.13 微米或以下的工艺流程。  | 功耗分析脚本                |

| 可测性度量                                |                                                         |                       |

| Fault Coverage                       | 在完成扫描链的插入后,计算 IP 故障覆盖率。                                 | 可测性脚本                 |

| IDDQ Coverage                        | 在完成扫描链的插入后,计算 IDDQ 的测试覆盖率。该度量一般被应用于 0.18 微米或以下的工艺流程中    | 可测性脚本                 |

| Number of Full Scan Chains           | 计算插入该 IP 的全扫描链的数目                                       | 可综合 RTL 代码, 可<br>测性脚本 |

#### 3) 评测输出

#### a) 代码质量检查报告

代码质量影响 IP 核的可重用性、可维护性和便携性。评测流程中采用了一个基于 LEDA 规则的代码质量度量标准来对代码质量进行检查。该质量标准包括了三个规则集合。在评测流程中定义了三个不同代码规则集合: VSIA QIP(包括了可综合性以及时钟、复位相关的规则),可读性和可测性规则。下图是 "RTL 代码风格检查"的表格。 在该表格中有三个不同代码检查规则集合。IP 的设计人员可以根据 IP 核的实际情况来宣称 IP 是否

遵循某个规则集合。而且可以从该规则集合中选择不适用于该 IP 的规则,并填写在该表格中。

| 1. RTL coding style                                            |                    |           |                                                                                                         |             |                  |                                                           |                  |             |

|----------------------------------------------------------------|--------------------|-----------|---------------------------------------------------------------------------------------------------------|-------------|------------------|-----------------------------------------------------------|------------------|-------------|

| Metirc: Compliance to QIP coding style                         | declaration        | Metiro:   | Compliance to Readability coding styl                                                                   | declaration | Metirc:          | Compliance to DFT                                         | coding style     | declaration |

| Description:  OP 2.0 coding style based on leda rule yes sets? |                    |           | Does the IP RTL source code support<br>the Readability coding style defined<br>based on leda rule sets? |             | Description:     | Does the IP RTL<br>support the DFT<br>defined based on le | coding style     | Yes         |

| Not Applicable Rules for QIP 2.0 (                             | oding style        | Not Ap    | plicable Rules for Readability coding s                                                                 | tyle        | ١                | lot Applicable Rules                                      | for DFT codin    | g style     |

| Rule Name Comments                                             |                    | Rule Name | Comments                                                                                                |             | <b>Rule Name</b> | Comments                                                  |                  |             |

| G_559_1 This IP using one block encode SM                      | $I \subset I$      |           |                                                                                                         |             |                  |                                                           |                  |             |

|                                                                | $\supset$          |           |                                                                                                         |             | 単循 该             | 规则集合                                                      | 的声               |             |

| 不                                                              | <b>─</b><br>适用于该 I | P 的规则3    | · · · · · · · · · · · · · · · · · · ·                                                                   | 明明          | <u> </u>         | 70L/17/C II                                               | н <b>у</b> /     |             |

|                                                                |                    |           |                                                                                                         |             |                  |                                                           |                  | <u> </u>    |

|                                                                |                    |           |                                                                                                         |             |                  |                                                           | , and the second |             |

#### b) 验证质量检查报告

验证质量主要采用代码覆盖率作为度量。在评测流程中,我们使用Synopsys公司的 VCS\_MX作为测量工具。

| 2. Verifi    | cation                                                                                   |                         |                      |                         |                       |           |     |      |  |  |

|--------------|------------------------------------------------------------------------------------------|-------------------------|----------------------|-------------------------|-----------------------|-----------|-----|------|--|--|

| Metrics:     | Metrics: line coverage, condition coverage, toggle coverage, fsm coverage, path coverage |                         |                      |                         |                       |           |     |      |  |  |

| Description: | Has every test case be                                                                   | en executed without e   | rror? And do you gen | erate any code coverage | reports for every tes | t suites? |     | Yes  |  |  |

|              |                                                                                          |                         | h                    | letrics reference value |                       |           |     |      |  |  |

|              | Ver                                                                                      | ification Configuration | n                    | Code coverage           |                       |           |     |      |  |  |

| ID           | Macros                                                                                   | File Sets               | Testbench top name   | line                    | condition             | toggle    | fsm | path |  |  |

| 1            |                                                                                          | 2,3                     | tb_test_top          |                         |                       |           |     |      |  |  |

|              |                                                                                          |                         |                      |                         |                       |           |     |      |  |  |

|              |                                                                                          |                         |                      |                         |                       |           |     |      |  |  |

|              |                                                                                          |                         |                      |                         |                       |           |     |      |  |  |

|              |                                                                                          |                         |                      |                         |                       |           |     |      |  |  |

#### c) 综合质量检查报告

在目前的评测流程中,设计质量度量只包括了对面积的评测。该度量主要针对可综合的电路,包括:逻辑单元面积(Total Cell Area)和互连面积(Net Connection Area)。对于布局布线阶段前的设计,互连面积度量只能是作为一个参考来使用

| 4. Synth     | <u>iesis</u>                                                                                                                                                          |                                   |              |                         |                 |            |                     |             |  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------|-------------------------|-----------------|------------|---------------------|-------------|--|

| Metrics:     | Estimated total cell ar                                                                                                                                               | ea, Estimated net conne           | ction area   |                         |                 |            |                     | declaration |  |

| Description: | Description: Can IP be synthesised into at least one library, the syntheis scripts, design constrains(SDC file) and area reports has been packaged into deliverables? |                                   |              |                         |                 |            |                     |             |  |

|              |                                                                                                                                                                       |                                   | ı            | Metrics reference value |                 |            |                     |             |  |

|              |                                                                                                                                                                       | Synthesis C                       | onfiguration |                         | total cell area |            | net connection area |             |  |

| ID           | library                                                                                                                                                               | sdc file path                     | metric cell  | phase                   | area            | gate count | area2               | gate count2 |  |

| 1            | SMIC 0.18                                                                                                                                                             | scripts/module_c<br>onstrains.tcl | NAND2X1      | Pre_Layout              |                 |            |                     |             |  |

|              |                                                                                                                                                                       |                                   |              |                         |                 |            |                     |             |  |

|              |                                                                                                                                                                       |                                   |              |                         |                 |            |                     |             |  |

|              |                                                                                                                                                                       |                                   |              |                         |                 |            |                     |             |  |

|              |                                                                                                                                                                       |                                   |              |                         |                 |            |                     |             |  |

#### d) 可测性检查报告

这里主要使用故障覆盖率和Iddq覆盖率作为可测性的主要度量指标。扫描路 径将被插入到可综合的设计中,一个测试向量生成工具将被应用到故障覆盖率和 Iddq覆盖率的测量中。

| 5. Testa | <u>bility</u>                                                                                                                                                                 |               |             |                           |            |            |                |               |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------|---------------------------|------------|------------|----------------|---------------|--|

| Metrics: | Metrics: fault coverage, iddq coverage                                                                                                                                        |               |             |                           |            |            |                |               |  |

|          | Description: Has the trial ATPG coverage(fault coverage or iddq coverage) been run and results made available? And test isolation requirements been addressed and documented? |               |             |                           |            |            |                |               |  |

|          |                                                                                                                                                                               |               |             | Metrics reference value   |            |            |                |               |  |

|          |                                                                                                                                                                               |               | Test Co.    | nfiguration               |            |            | fault coverage | iddq coverage |  |

| ID       | library                                                                                                                                                                       | test strategy | chain count | scan style                | test clock | phase      | value          | value2        |  |

| 1        | SMIC 0.18                                                                                                                                                                     | full_scan     | 3           | multiplexed_flip_flo<br>p | clk        | Pre_Layout |                |               |  |

|          |                                                                                                                                                                               |               |             |                           |            |            |                |               |  |

|          |                                                                                                                                                                               |               |             |                           |            |            |                |               |  |

|          |                                                                                                                                                                               |               | ·           |                           |            |            |                |               |  |

|          |                                                                                                                                                                               |               |             |                           |            |            |                |               |  |

#### e) 形式化验证报告

形式化检查主要应用于 RTL 设计和相应的网表实现之间。该检查可以用数学的方法来证明两者之间的等价性。通过该度量可以确保 IP 核能够在不同的工艺库间得到正确的综合结果。

| 3. Form      | al Methods                                   |                |                |  |  |  |  |  |

|--------------|----------------------------------------------|----------------|----------------|--|--|--|--|--|

| Metrics:     | Metrics: Equivalence checking failing points |                |                |  |  |  |  |  |

| Description: | Yes                                          |                |                |  |  |  |  |  |

|              | Metrics re                                   | eference value |                |  |  |  |  |  |

|              | Formal Verification                          |                | failing points |  |  |  |  |  |

| ID           | Ref. Level                                   | Impl. Level    | value          |  |  |  |  |  |

| 1            | rtl_level                                    | gate_level     | 0              |  |  |  |  |  |

|              |                                              |                |                |  |  |  |  |  |

|              |                                              |                |                |  |  |  |  |  |

#### f) 性能检查报告

性能检查的度量主要是从时序分析的报告中抽取时序上的冲突。这里可以使用时序覆盖率(Timing Coverage)来作为一个概要的度量,具体的信息将存放在时序分析的报告中。实际上,一个 IP 核只有满足给定的时间约束才能算是通过最终的评测。在自动化的评测流程中,我们使用 PrimeTime 来进行时序分析。

| 6. Timin     | <u>ıq</u>                                                                                                                                                                                                                                       |                       |                      |                          |                     |                 |                        |             |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|--------------------------|---------------------|-----------------|------------------------|-------------|--|

| Metrics:     | setup timing coverage,                                                                                                                                                                                                                          | hold timing coverage, | minplus width timing | coverage, recovery timin | ig coverage removal | timing coverage |                        | declaration |  |

| Description: | Description. Have you assured all timing requirements satified and timing constraints files do not define timing requirements between signals for which there is no actual connecting logic? Are the scripts and timing check results provided? |                       |                      |                          |                     |                 |                        |             |  |

|              |                                                                                                                                                                                                                                                 |                       | ,                    | Metrics reference value  | :                   |                 |                        |             |  |

|              |                                                                                                                                                                                                                                                 | Timing Configuration  |                      |                          | Ti                  | ming coverage   |                        |             |  |

| ID           | library                                                                                                                                                                                                                                         | timing constrain path | phase                | setup                    | hold                | minplus width   | гесочегу               | removal     |  |

|              |                                                                                                                                                                                                                                                 |                       |                      |                          |                     |                 |                        |             |  |

|              |                                                                                                                                                                                                                                                 |                       |                      |                          |                     |                 |                        |             |  |

|              |                                                                                                                                                                                                                                                 |                       |                      |                          |                     |                 |                        |             |  |

|              |                                                                                                                                                                                                                                                 |                       |                      |                          |                     |                 |                        |             |  |

|              |                                                                                                                                                                                                                                                 |                       |                      |                          |                     |                 |                        |             |  |

|              |                                                                                                                                                                                                                                                 |                       |                      |                          |                     |                 |                        |             |  |

| Metric:      | False Path                                                                                                                                                                                                                                      |                       | Metric:              | : Timing borrow path M   |                     |                 | tric: Multicycle Paths |             |  |

| Description: |                                                                                                                                                                                                                                                 |                       | Description:         |                          |                     | Description     |                        |             |  |

|              | Path Declaratio                                                                                                                                                                                                                                 | n                     | Path Declaration     |                          |                     | F               | Path Declaration       |             |  |

| From         | To                                                                                                                                                                                                                                              | Through               | From                 | To                       | Through             | From            | To                     | Through     |  |

|              |                                                                                                                                                                                                                                                 |                       |                      |                          |                     |                 |                        |             |  |

#### g) 功耗检查报告

功耗检查包括两大类度量:最坏情况功耗和实际情况功耗。最坏情况功耗的度量使用 ATPG 的测试向量来进行测量。而为了给出实际情况功耗的度量值,IP 的提供商必须在 IP 的可交付项中包括符合实际应用情况的测试向量。

#### (1) 实际功耗分析

| 7. Applic   | ation Pattern Po                                                                                                                                                     | ower Analysis |           |                      |             |               |          |            |                   |       |          |        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------|----------------------|-------------|---------------|----------|------------|-------------------|-------|----------|--------|

| Metrics:    | Metrics: application pattern peak power, application pattern dynamic average power, application pattern static average power                                         |               |           |                      |             |               |          |            |                   |       | declarat |        |

| Description | Description Has the application pattern power analysis done? and have you assured all power requirements satified? Are the scripts and power check results provided? |               |           |                      |             |               |          |            |                   | No    |          |        |

|             | Metrics reference value                                                                                                                                              |               |           |                      |             |               |          |            |                   |       |          |        |

|             | Power configuration peak power average                                                                                                                               |               |           |                      |             |               |          |            | power             |       |          |        |

| ID          | transition (ns)                                                                                                                                                      | interval (ns) | library   | design instance name | tb top name | sim config ID | VCD/SAIF | Clock Name | Clock Period (ns) | value | dynamic  | static |

| 1           | 0.1                                                                                                                                                                  | 10            | SMIC 0.18 |                      | tb_spi_top  | 1             | SAIF     |            | 7                 |       |          |        |

#### (2) ATPG 功耗分析

| 8. ATPG                                                                                                                                                         | Pattern Power                                                                                                       | 'Analysis     |           |          |            |                   |       |           |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------|-----------|----------|------------|-------------------|-------|-----------|--------|

|                                                                                                                                                                 | Metrics: atpg pattern peak power, atpg pattern dynamic average power, atpg pattern static average power declaration |               |           |          |            |                   |       |           |        |

| Description: Has the atpg pattern power analysis done? and have you assured all power requirements satisfied? Are the scripts and power check results provided? |                                                                                                                     |               |           |          |            |                   |       | Yes       |        |

|                                                                                                                                                                 | Metrics reference value                                                                                             |               |           |          |            |                   |       |           |        |

|                                                                                                                                                                 | Power configuration peak power aver                                                                                 |               |           |          |            |                   |       | age power |        |

| ID                                                                                                                                                              | transiton (ns)                                                                                                      | interval (ns) | library   | VCS/SAIF | Clock Name | Clock Period (ns) | value | dynamic   | static |

| 1                                                                                                                                                               | 0.1                                                                                                                 | 10            | SMIC 0.18 | SAIF     | clk        | 7                 |       |           | ·      |

## 3. 数字软 IP 核 FPGA 验证评测(类别三)

#### 1) 流程

FPGA 设计验证的基本流程如下:

- 1. 设计方案

- 2. 编码或原理图输入

- 3. RTL 级仿真(模块级和系统级)

- 4. 综合、布局布线

- 5. 静态时序分析

- 6. 动态时序仿真

- 7. 加载与调试

图 1 FPGA 验证流程图

FPGA 验证成为 SoC 设计流程中重要的一个环节,一方面作为硬件验证工具,

可以将所设计的 RTL 级代码综合实现后写入 FPGA 芯片进行调试检错;另一方面可以进行软件部分的并行开发,在验证板上检测驱动程序、启动操作系统。FPGA 验证的流程相当于一个 FPGA 设计的主要流程,它主要分为设计输入、综合、功能仿真(前仿真)、实现、时序仿真(后仿真)、配置下载、下载后板级调试检错这几个步骤。总的来说,FPGA 验证是整个 SoC 设计中一个重要而且有效的验证步骤,用来改进 RTL 级设计代码,验证功能的正确和完整性,提高 SoC 流片成功率。图 2 为 FPGA 验证平台。

图 2 FPGA 验证平台

#### 2) 度量定义

表 1 FPGA 度量定义表

| 度量名称      | 说明                                                                                                  | 相关的交付项                                           |

|-----------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------|

| 设计功能度量    |                                                                                                     |                                                  |

| IP 核功能的度量 | 针对IP核验证所需的FPGA的容量和<br>功能及性能上的需求。                                                                    | FPGA 的选型及使用<br>说明文档                              |

|           | 用以完成 IP 核 FPGA 功能验证的实现。                                                                             | IP 核 FPGA 功能验证<br>EDA 工具的使用及相<br>应的脚本和其说明文<br>档。 |

|           | ASIC 和 FPGA 物理结构上的不同,决定了 ASIC 代码需要一定的修改才能移植到 FPGA 上。但应该注意到这只是由于物理结构不同而对代码进行的转换,并不改变其功能。用以完成 IP核的综合。 | 可 FPGA 综合的 RTL<br>代码                             |

| 用以对 IP 核 FPGA 验证的平台移植、<br>功能的测试用途。 | FPGA 引脚约束文件<br>和接口说明文档 |

|------------------------------------|------------------------|

| 为16日被14月处。                         | 7四女旦 処男人信              |

| 用以确定对 IP 核验证流程                     | IP 核的 FPGA 功能验         |

|                                    | 证参考流程及方法。              |

| 用以完成对 IP 核功能的全面验证。对                | FPGA 功能验证列表:           |

| 其功能给出一个定性和定量的判断。                   | 包括                     |

|                                    | (一) 功能测试项内容            |

|                                    | (二) 单项测试所用的            |

|                                    | 到的软件和硬件                |

|                                    | 的激励                    |

|                                    | (三) 单项测试的响应            |

|                                    | 描述和捕获方法                |

|                                    | (四) 测试中发现的设            |

|                                    | 计问题和缺陷                 |

|                                    | FPGA 验证软件环境:           |

|                                    | 包括                     |

|                                    | 1、IP集成用的RTOS           |

|                                    | 2、 测试软件源码及             |

|                                    | 可执行文件及其                |

|                                    | 连接库。                   |

|                                    | FPGA 验证硬件环境:           |

|                                    | FPGA 验证平台,如有           |

|                                    | 须提供,以及测试用              |

|                                    | 的特殊仪器及使用说              |

|                                    | 明,作参考平台建设              |

|                                    | 用。                     |

|                                    | 第三方参考文件:指              |

|                                    | 由用户或者其他第三              |

|                                    | 方独立组织所提供的              |

|                                    | 测试结果或用户报               |

|                                    | 告,也包括一些 IP 应           |

|                                    | 用和集成的成功案               |

|                                    | 例。                     |

|                                    | V 4 9                  |

# 3) 评测输出

| 度量名称     | 功能说明   | 相关度量的报告  |  |  |

|----------|--------|----------|--|--|

| 设计功能度量   |        |          |  |  |

| IP 核功能 X | 功能X的说明 | 实测功能是否吻合 |  |  |

# 4. 数字软 IP 核硅形态验证评测(类别四)

#### 1) 流程

硅验证的基本流程如下:

- 1. 环境搭建

- 2. 芯片基本功能测试

- 3. 数字软 IP 核功能测试

- 4. 数字软 IP 核性能测试

- 5. 功耗分析

- 6. 填写报告

#### 2) 度量定义

表 1 数字软 IP 核硅验证度量定义表

| 度量名称              | 说明                                                 | 相关的交付项                                                                   |

|-------------------|----------------------------------------------------|--------------------------------------------------------------------------|

| 数字软IP核硅验证测试度<br>量 |                                                    |                                                                          |

| 测试芯片基本功能测试        | 对数字软 IP 核的硅化设计进行验证,以确保后续测试项的可测性和可信度                | 硅验证的说明文档 硅验证环境参考: 测试软件、硬件、通讯接口、测试用的特殊仪器及相关说明。 数字软 IP 核硅化设计文档、结构框图及各管脚说明  |

| 数字软 IP 核功能测试      | 数字软 IP 核所要实现的功能进行测试,包括各种工作模式下的数字软 IP 核功能           | 数字软 IP 核能测试说明文档 特殊功能测试须提供相关测试 指南 如有数字软 IP 核设计手册或设计厂家自己进行的测试报告,也可提供作为测试参考 |

| 数字软 IP 核性能测试      | 数字软 IP 核所要实现的性能进行测试,包括不同工作模式,不同工艺模型,不同工作环境模型下的性能测试 | 数字软 IP 核性能测试说明文档 特殊性能测试须提供相关测试指南 如有数字软 IP 核设计手册或设计厂家自己进行的测试报告,也可提供作为测试参考 |

| 功耗分析              | 通过对测试芯片的功耗测试, 对芯                                   | 数字软 IP 核功耗测试说明文                                                          |

| 片内数字软 IP 核的功耗进行分析, | 档               |

|--------------------|-----------------|

| 包括不同工作模式,不同工艺模型,   | 特殊环境模式下的测试须提供   |

| 不同工作环境模型下的性能测试     | 相关测试指南          |

|                    | 如有数字软 IP 核设计手册或 |

|                    | 设计厂家自己进行的测试报    |

|                    | 告,也可提供作为测试参考    |

# 3) 评测输出

表 2 数字软 IP 核硅验证输出表

| 次1 次1 次起短曲幅以 |          |                                |  |  |  |  |  |

|--------------|----------|--------------------------------|--|--|--|--|--|

| 度量名称         | 功能说明     | 相关度量的报告                        |  |  |  |  |  |

| 设计功能度量       |          |                                |  |  |  |  |  |

| 测试芯片基本功能 X   | 功能 X 的说明 | 实测功能是否吻合                       |  |  |  |  |  |

| 数字软 IP 核功能 Y | 功能Y的说明   | 实测功能是否吻合                       |  |  |  |  |  |

| 数字软 IP 核性能 Z | 性能Z的说明   | 实测数据是否达到标称值,多大程度<br>上落后或者超过标称值 |  |  |  |  |  |

三、 附件一(申请书)

编号: 密级:公开

# 信息产业部软件与集成电路促进中心

# 标准化 IP 核认证服务申请书

| 申请单位(公章): _  |  |

|--------------|--|

| IP 核名称 (编号): |  |

|              |  |

| 申请日期:        |  |

信息产业部软件与集成电路促进中心

## 填表要求

请按如下要求填写/提交申请表单:

- 1) 申请表一律要求用计算机填写,内容应真实、具体。

- 2) 如填写内容较多,可另加附页。

- 3) 提交申请时准备两份纸版,同时交电子版一份(光盘)。

# 申请单位基本情况

| 申请单位全称 | (中文):  |  |

|--------|--------|--|

| 申请单位全称 | (英文):  |  |

| 地址:    |        |  |

|        |        |  |

| 法定代表人: |        |  |

| 联系人姓名: |        |  |

| 联系方式:  | 电话:    |  |

|        | 传真:    |  |

|        | 手机:    |  |

|        | Email: |  |

# IP 核概况

| IP 核名称                                  |                       |      |        |       |     |     |           |     |         |              |     |     |     |          |

|-----------------------------------------|-----------------------|------|--------|-------|-----|-----|-----------|-----|---------|--------------|-----|-----|-----|----------|

| 编号/版本号                                  |                       |      |        |       |     |     |           |     |         |              |     |     |     |          |

| 开                                       | 发工具                   |      |        |       |     |     | 验证        | 环境  |         |              |     |     |     |          |

|                                         | □软核                   | IP   | 申      |       | 类别一 | •   |           | l.  |         |              |     |     |     |          |

| IP核                                     | □模拟                   | ΙÞ   | 请的     |       | 类别二 | •   |           | □其它 | '雲運     | <b>三哈</b> 证: | 佰   |     |     |          |

| 类型                                      | □ ( <del>X</del> ) (X | 11   | 认      |       | 类别三 |     |           |     | 11111 9 | , J.W. M.    | · X |     |     |          |

|                                         | □硬核                   |      | 证 □类别四 |       |     |     |           |     |         |              |     |     |     |          |

| IP核                                     |                       |      |        | 应用    |     |     | 系统应       |     |         | 电子           |     |     |     | 接口       |

| 领域及                                     | :行业                   | □移   | 动通     | 信     | □信. | 息安全 | <u> </u>  | 联网络 | } L     | ]存储          | 设备  | - [ | □其他 | <u>.</u> |

| IP 核基本描述及特点                             | IP 核<br>基本<br>描述      |      |        |       |     |     |           |     |         |              |     |     |     |          |

| #述及特点                                   | IP核<br>特点<br>以功能      |      |        |       |     |     |           |     |         |              |     |     |     |          |

| 简要打<br>认证 <u></u>                       |                       |      |        |       |     |     |           |     |         |              |     |     |     |          |

| 认证 IP<br>产权i<br>(专利 <sup>3</sup><br>及所属 | 说明<br>列表以             |      |        |       |     |     |           |     |         |              |     |     |     |          |

| 认证结果                                    | 果发布                   | 是否是否 |        |       |     | 挂牌推 | È) T      |     | [       | □ 是<br>□ 是   |     |     | 否   |          |

| 应准备的                                    |                       | 要求   | 参见     | Ľ ≪IP | 核评测 | 和验证 | —<br>E类别》 | ,   |         |              |     |     |     |          |

#### 申请单位声明

本单位自愿申请信息产业部软件与集成电路促进中心对\_\_\_\_\_进行标准化 IP 核认证,并承担下列义务:

- (1) 按信息产业部软件与集成电路促进中心《标准化 IP 核认证服务申请指南》中的要求履行有关责任和程序。

- (2) 本单位将预付本次认证服务所需的费用,并按信息产业部软件与集成电路促进中心签署技术服务合同规定支付。

申请单位法定代表人(签名): 申请单位(盖章)

年 月 日

# 四、附件二

# 数字软 IP 交付项

M-Mandatory, 强制项 R-Recommended, 推荐项

CM-Conditional Mandatory,条件强制项

CR-Conditional Recommended, 条件推荐项

| IP 交付项     | 格式                  | 重要性 | 备注                                                                                                      |

|------------|---------------------|-----|---------------------------------------------------------------------------------------------------------|

| 文档交付项      |                     |     |                                                                                                         |

| 交付项清单      | PDF, HTML,<br>ASCII | R   | IP 集成者在 IP 交易时可以根据交付项清单来检查 IP 交付项的完整性                                                                   |

| IP 概述文件    | PDF, HTML,<br>ASCII | M   | 为了方便 IP 的快速评估,该概述文件只对 IP 进行简洁的描述。                                                                       |

| 标准证明文件     | PDF, HTML,<br>ASCII | CR  | 如果 IP 是基于某类工业标准或协议进行设计的,则 IP 设计者须提供该 IP 的标准或协议兼容性的证明 文件                                                 |

| IP 模块指南    | PDF, HTML,<br>ASCII | СМ  | IP 模块指南主要给 IP 集成者提供关于该 IP 的 I/O、存储器映射、内部寄存器和功能描述的信息。                                                    |

| 处理器 IP 核指南 | PDF, HTML,<br>ASCII | СМ  | 处理器 IP 核指南主要给 IP 集成者提供关于该 IP 的 I/O、存储器映射、指令集描述、寄存器堆和中断与 异常处理的信息。                                        |

| IP 集成指南    | PDF, HTML,<br>ASCII | M   | IP 集成指南主要描述该 IP 进行 SoC 集成设计时的相关信息。这些信息包括接口属性、功耗与面积、综合过程描述等。充足而详细的信息有助于对 SoC 设计者进行指引。                    |

| IP 测试指南    | PDF, HTML,<br>ASCII | М   | IP 测试指南主要给 IP 集成者提供关于测试插入和<br>实现的相关信息。这些信息包括测试 wrapper、 测<br>试 patterns、DFT 结构和测试脚本等。                   |

| 验证指南       | PDF, HTML,<br>ASCII | M   | IP 验证指南主要提供验证策略和验证平台的相关信息,以便于 IP 集成者进行功能验证。这些信息包括 test bench、drivers 和 monitors、验证模型、激励和测试码、仿真脚本、验证方法等。 |

| 版本信息文件     | PDF, HTML,<br>ASCII | M   | 版本信息文件记录了关于 IP 的描述变化以及相应<br>版本发布的历史信息。                                                                  |

| IP 问题报告    | PDF, HTML,<br>ASCII | R   | IP 问题报告记录了该 IP 应用时存在的各种问题。                                                                              |

| N 554 N 554 N 554 N   |                                 |    | 国家 IP 核标准符合性评测与认证指南                                                                                         |

|-----------------------|---------------------------------|----|-------------------------------------------------------------------------------------------------------------|

| 支持信息报告                | PDF, HTML,<br>ASCII             | R  | 支持信息报告包含了 IP 供应商详细的联系方式、所有权申明、术语表、责任申明、兼容性申明和质量申明等内容。                                                       |

| 代码检查交付项               |                                 |    |                                                                                                             |

| 目录结构文件                | PDF, HTML,<br>ASCII             | M  | 基于通用标准目录结构组织的 IP, 在相同环境下具有即插即用能力, 具有很好的重用性。                                                                 |

| 命名规范文件                | PDF, HTML,<br>ASCII             | R  | IP package 中需要包括一个统一的命名规范文件.                                                                                |

| RTL 代码风格规范文<br>件      | PDF, HTML,<br>ASCII             | СМ | 代码风格文件将确保源代码的可读性和可理解性                                                                                       |

| 可配置 rule-set 文件       | 脚本文件                            | CR | 可配置 rule-set 文件包含了代码风格的规则                                                                                   |

| 代码风格检查脚本              | 脚本文件                            | CM | 代码风格检查脚本作为代码检查工具的输入使用。                                                                                      |

| 代码风格检查的 Setup<br>环境文件 | 脚本文件                            | СМ | Setup 环境文件是 EDA 工具进行代码风格检查时的辅助文件。                                                                           |

| 系统设计交付项               |                                 |    |                                                                                                             |

| 系统评估模型                | C/C++, VHDL,<br>Verilog, Matlab | CR | IP 用户在进行系统设计时,可以利用系统模型进行 IP 的评估和选择。该模型是非周期精度的模型。                                                            |

| 行为模型                  | C/C++, VHDL,<br>Verilog         | M  | 行为模型用于单独 IP 的功能验证、IP 集成和软硬件协同验证。行为模型是基于周期精度的模型,该模型不包含 IP 内部的详细信息。                                           |

| 逻辑设计交付项               |                                 |    |                                                                                                             |

| 可综合的 RTL 源代码          | Verilog,<br>VHDL, PLI           | M  | 可综合的 RTL 源代码精确描述了软核 IP 的功能。<br>该代码在 EDA 工具的支持下可以被综合和仿真。<br>可综合的 RTL 源代码可以看作基于标准 RTL 语言<br>描述、具有周期精度的 IP 模型。 |

| 源代码编译顺序文件             | Tcl 脚本                          | R  | 源代码编译顺序文件记录了 IP 各模块进行编译时<br>的次序关系。.                                                                         |

| 综合脚本                  | DC shell 脚本,<br>Tcl 文件          | M  | 综合脚本作为 EDA 综合工具的输入使用.                                                                                       |

| 综合约束                  | DC shell 脚本,<br>Tcl 文件          | R  | 综合约束文件描述了综合相关的约束信息,包括时<br>序约束、功耗约束和面积约束等信息.                                                                 |

| 综合 setup 环境文件         | Tcl 脚本                          | M  | Setup 环境文件是 EDA 工具进行综合时的辅助文件。                                                                               |

| 布局规划信息文件              | PDEF, LEF,<br>SDF               | CR | 布局规划信息文件能对系统 IC 设计者提供帮助。<br>这些信息主要包括布局规划约束、互联约束、<br>location 约束、块信息和 pin 信息等。                               |

| 测试和制造相关的交付            | 寸项                              |    |                                                                                                             |

| DFT 脚本                | Tcl 脚本                          | R  | DFT 脚本作为 EDA 可测性工具的输入使用。                                                                                    |

| DFT Setup 环境文件        | Tcl 脚本                          | R  | Setup 环境文件是 EDA 工具进行可测性设计时的辅助文件。                                                                            |

| ATPG 脚本               | Tcl 脚本                          | R  | ATPG 脚本作为 EDA 自动测试图形产生工具的输入使用                                                                               |

|                              |                     |    | 四多 IF 核物性打造性机构与 从此指用                                                                       |

|------------------------------|---------------------|----|--------------------------------------------------------------------------------------------|

| ATPG setup 环境文件              | Tel 脚本              | R  | ATPG 环境文件是 EDA 工具进行自动测试图形产生时的辅助文件。                                                         |

| 设计规则检查文件                     | STIL 文件             | R  | 测试规则检查文件记录了可测性设计过程中需要<br>遵守的设计规则(如 build 规则、时钟规则、网表<br>规则,路经延迟规则等)。                        |

| 测试 Wrappers                  | Verilog, VHDL       | R  | 测试 Wrappers 负责将测试序列转换成测试图像,用于 IP 的测试。如果交付基于工业标准,如 IEEE P1500 的测试 Wrapper,会加快 SoC 的集成和测试过程。 |

| 功能验证交付项                      |                     |    |                                                                                            |

| Testbench                    | 多格式文件               | М  | 验证 testbench 交付项包括验证 IP 功能和时序所需的模块和元件。Testbench 的构造要便于 IP 的 RTL 模型(RTL 源代码)验证。             |

| Monitors                     | Verilog, VHDL,      | M  | Monitors 用来探测协议错误和监视仿真结果。                                                                  |

| 详细的 memory 行为模型              | Verilog, VHDL,      | CR | 详细的 memory 行为模型用来确保仿真过程中 IP 模块执行正确的功能。                                                     |

| HDL 接口模型                     | Verilog, VHDL,      | R  | HDL 接口模型是用来描述 IP 与外围环境相关操作的器件模型。                                                           |

| 激励                           | ASCII, 目标代<br>码, 约束 | M  | 激励是基于 testbench 上运行的一套用于功能验证的测试向量(test cases)。                                             |

| 仿真脚本                         | 脚本、ASCII            | M  | 仿真脚本作为 EDA 仿真工具的输入使用。                                                                      |

| 代码覆盖率                        | 脚本、ASCII            | R  | 代码覆盖率可以用来测量激励的质量。代码覆盖率 包括行覆盖率、触发覆盖率、条件覆盖率等。                                                |

| 功能覆盖率                        | 脚本、配置文件             | R  | 功能覆盖率用来测量设计规范中的各种特征被满足的程度。                                                                 |

| 形式等效性检查                      | 配置文件,脚本,约束          | R  | 形式等效性检查交付项用来验证 RTL 代码和网表之间的逻辑等效性。                                                          |

| 形式模型检查                       | 配置文件、脚本             | R  | 形式模型检查交付项通过形式数学方法来验证 IP 的功能属性。                                                             |

| Emulation                    | 多格式文件               | R  | Emulation 交付项包含 IP 模块在 emulator 仿真器上进行仿真所需的文件和数据。                                          |

| 时序和功耗分析相关的                   | り交付项                |    |                                                                                            |

| 时序分析 Setup 环境文<br>件          | 配置文件                | R  | Setup 环境文件为 EDA 工具进行时序分析时的辅助文件                                                             |

| 时序分析脚本                       | 脚本                  | R  | 时序分析脚本作为 EDA 静态时序分析工具的输入<br>使用。                                                            |

| User-defined switching<br>文件 | 配置文件                | R  | User-defined switching 文件包含了 IP 供应商为进行 功耗分析而定义的开关活动情况。                                     |

| SAIF 文件                      | SAIF 文件             | R  | SAIF 文件为用于基于开关活动功耗计算的开关活动交互格式文件(Switching activity interchange format file)。               |

| VCD 文件          | VCD 文件 | R | VCD 文件包含用于功耗计算的基于事件的开关活动信息。       |

|-----------------|--------|---|-----------------------------------|

| 功耗分析环境 Setup 文件 | 脚本     | R | 环境 Setup 文件为 EDA 工具进行功耗分析时的辅助 文件。 |

| 功耗分析脚本          | 脚本     | R | 功耗分析脚本作为 EDA 功耗分析工具的输入使用。         |

#### 注释:

- 1. 如果IP 不含一个处理器核,则IP 模块指南交付项为强制项。

- 2. 如果IP 在功能上是一个处理器核或者IP 包含一个处理器核,则处理器IP 核指南交付项为强制项。

- 3. 如果需要进行RTL代码风格检查,则RTL代码风格规范文件、代码风格检查脚本文件、 代码风格检查 setup 环境文件为强制项。并且如果可配置 rule-set 文件存在的话,该文件 为推荐项。但是,即使所有的交付项都提供的话,还需要一些人工的工作才能进行代码 风格检查。

- 4. 系统仿真模型不需满足基于周期的精度。交付该项的必要性取决于 IP 功能的复杂度和 SoC 集成的要求。

- 5. 只有系统IC 设计者需要IP 的布局规划信息。这些信息包括块信息、pin 信息、location 约束、 Mega-cell 信息如RAM 等等 。由于布局规划信息是工艺库相关的,所以只有当 SoC 设计者需要时,它才为推荐项。

详细的行为模型包括 memory 模型 (RAM 和 ROM) 。当 IP 中包含嵌入式 memory, 则 C 和 Verilog 的 memory 模型属于推荐项。